3나노 세계 최초 선언했지만...삼성전자, 3나노 선두에도 고민삼성 고객사 퀄컴, 하반기 전략 칩 '스냅드래곤' TSMC에 생산 맡겨외신 "TSMC 9월 핀펫 기반 3나노 양산 시작"···GAA 삼성과 대조3나노 TSMC 첫 고객인 애플, PC용 SOC M2 생산 예고

세계 1위 파운드리(반도체 위탁생산) TSMC가 3나노(1㎚는 10억분의 1m) 양산 초읽기에 들어갔다. 세계 최초로 양산한 삼성전자의 후발주자로 나선 것이다.

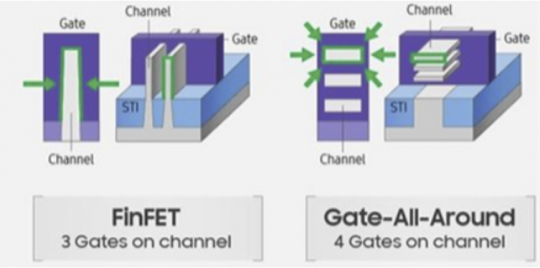

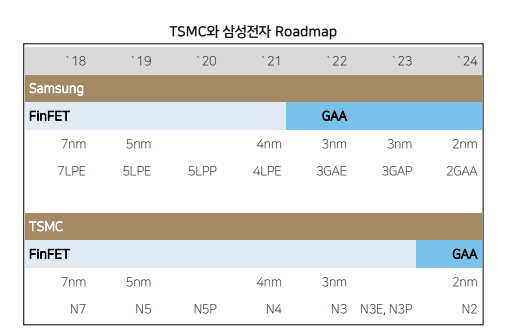

TSMC는 삼성과 달리 핀펫(FinFET) 트랜지스터를 유지했다. 삼성전자가 선택한 GAA(Gate-All-Around) 트랜지스터는 핀펫의 구조적 한계를 극복하는 차세대 트랜지스터로 알려졌는데 이를 채택하지 않은 것이다. 파운드리 패권을 두고 3나노 공정부터 양사의 로드맵이 뒤바뀐 셈이다. TSMC의 핀펫은 세대가 거듭할수록 기술력이 크게 확대된 것으로 파악돼 파운드리 1위를 노리는 삼성전자에게 녹록지 않은 상황이다.

◆삼성 품에서 퀄컴 떠났는데...TSMC 3나노 양산 초읽기 = 삼성전자는 당초 예고한 대로 지난 6월30일 세계 최초로 GAA 기술을 적용한 3나노 양산을 공식 발표했고 지난달 말에는 제품 출하식까지 열었다. 이는 로드맵에서 TSMC를 앞선 것으로 삼성 파운드리에 기념비적인 결과로 기록됐다. 하지만 '축포'에도 삼성전자의 고민이 깊어지고 있다.

IT 소식에 정통한 궈밍치 대만 TF인터내셔널 연구원에 따르면 삼성전자의 최대 고객사인 퀄컴은 하반기 플래그십(최고급) AP(애플리케이션프로세서)인 스냅드래곤8+ Gen 1(1세대)' 생산을 TSMC에 맡겼다. 삼성전자 입장에선 고객사 일감을 경쟁사에 빼앗긴 셈이다. 퀄컴은 올해 1분기 삼성전자의 분기 보고서에서 5대 매출처에 처음 등장했으며 전작인 스냅드래곤8 생산물량을 삼성전자에 몰아줬다.

TSMC의 3나노도 걱정거리다. 대만 정보기술(IT)매체 디지타임스 등은 TSMC가 9월부터 3나노 핀펫을 적용해 애플의 PC용 시스템 온 칩(SoC : System on Chip) M2를 생산한다고 밝혔다. 핀펫은 윗면과 좌·우 3면의 게이트가 둘러싸 누설전류를 막아주지만 GAA는 아랫면까지 총 4면의 게이트로 감싸 누설전류를 보다 세밀하게 제어할 수 있다.

3나노부터 양사의 선택지가 엇갈린 것으로 TSMC는 핀펫, 삼성전자는 GAA로 고객사 확보에 집중할 계획이다. 하지만 삼성전자는 4나노 수율(완성품 중 합격품 비율) 확보에도 어려움을 겪은 것으로 조사돼 상대적으로 조급해질 수밖에 없는 상황이다. TSMC의 3나노 수율이 기대 이상일 경우 고객사 확대에 어려움이 따를 것으로 보인다.

◆TSMC, 3나노 핀펫 기술력 입증···소비전력 30%까지 늘려 = 시장조사업체 트렌드포스에 따르면 올해 1분기 TSMC의 파운드리 점유율은 53.6%, 삼성전자는 16.3%로 집계됐다. 점유율 격차는 1개 분기 만에 3.5%포인트 벌어졌다. 트렌드포스는 삼성전자에 대해 "4나노 생산 확대와 수율 개선 속도가 예상만큼 빠르게 진행되지 않고 있다"고 설명했다.

TSMC의 핀펫 기술력은 이미 결과로 입증됐다. 애플은 "M2는 M1 대비 CPU(중앙 처리 장치) 속도는 18%, GPU(그래픽 처리 장치) 성능은 35% 향상됐다"며 "트랜지스터는 25% 확장돼 200억개를 사용하고 메모리 대역폭도 50% 확장됐다"고 밝혔다. M2, M1 모두 5나노 방식으로 생산되었는데 성능 차이가 크게 벌어진 이유는 공정 방식이 변화했기 때문이다.

M1과 M2는 TSMC의 5나노 1세대 공정인 'N5'와 2세대 'N5P'가 각각 채택됐다. 두 공정 모두 칩 사이즈는 동일하지만 N5P는 N5 대비 소비 전력은 10%, 성능은 5% 이상 개선됐다. TSMC의 파운드리 로드맵은 N7(7나노), N5(5나노), N3(3나노) 등 나노에 따라 공정 숫자가 바뀌며 같은 공정이라도 세대가 달라지면 숫자 뒤에 알파벳을 붙여 구분한다.

3나노 수준은 더욱 끌어올린 것으로 알려졌다. 미국 하드웨어 전문 매체 아난드테크(Anandtech)에 따르면 N3는 N5 대비 소비 전력은 25~30% 줄이고 성능은 10% 이상 끌어올렸다. 또 트랜지스터 밀도도 1.7배 증가했다. 트랜지스터는 전류가 흐르는 채널과 채널을 제어하는 게이트로 구분되는데 밀도가 높을수록 전력 효율을 높일 수 있다.

반도체 기술력의 핵심은 회로의 선폭을 얼마만큼 좁히는지에 달렸다. 선폭이 작을수록 소비전력은 감소하고 처리 속도가 빨라지기 때문이다. 또 웨이퍼의 크기가 동일하더라도 나노 숫자가 낮을수록 반도체 생산량도 증가한다. 다만, 생산성은 수율이 좌우한다. 4나노 생산에도 어려움을 겪은 삼성전자로선 TSMC의 3나노 수준을 걱정해야 하는 것이다.

삼성전자는 GAA 3나노 수율을 공식적으로 밝히지 않고 있다. 다만 삼성전자 관계자는 "양산의 의미는 회사마다 결정한 기준치를 충족한 것"이라고 설명했다. 수율이 확보되지 않으면 고객사에 약속한 물량을 제때 공급해주지 못하는 문제가 생길 수밖에 없어 3나노 패권 전쟁을 두고 삼성전자와 TSMC의 경쟁이 본격화될 것으로 보인다.

다만, 삼성전자는 파운드리 경쟁력에 자신감을 내비치며 '꿀릴 게 없다'는 입장이다. 사측은 2분기 콘퍼런스콜에서 '3나노 GAA 2세대 공정 개발현황과 고객사'에 대한 질문에 "2세대 공정은 1세대 대비 면적, 성능, 전력효율을 개선한 공정"이라며 "개발체계 개선을 통한 단계별 개발검증 강화, 개발초기 리소스 집중 투입을 통해 초기 수율 램프업(생산량 확대) 했다"고 설명했다.

또 "2024년 양산을 목표로 계획대로 진행 중"이라며 "특히 모바일 부문에서 복수의 대형 고객사를 이미 확보했고 HPC, 모바일 고객과 수주 관련 논의 중이고 규모는 점차 확대될 것이라고 기대한다"고 밝혔다.

관련기사

뉴스웨이 김현호 기자

jojolove7817@newsway.co.kr

저작권자 © 온라인 경제미디어 뉴스웨이 · 무단 전재 및 재배포 금지

댓글